# Shared Memory Multiprocessor Support for Functional Array Processing in SAC

#### CLEMENS GRELCK

Universität zu Lübeck Institut für Softwaretechnik und Programmiersprachen Ratzeburger Allee 160, 23538 Lübeck, Germany (e-mail: grelck@isp.uni-luebeck.de)

#### Abstract

Classical application domains of parallel computing are dominated by processing large arrays of numerical data. Whereas most functional languages focus on lists and trees rather than on arrays, SAC is tailor-made in design and in implementation for efficient high-level array processing. Advanced compiler optimizations yield performance levels that are often competitive with low-level imperative implementations.

Based on SAC, we develop compilation techniques and runtime system support for the compiler-directed parallel execution of high-level functional array processing code on shared memory architectures. Competitive sequential performance gives us the opportunity to exploit the conceptual advantages of the functional paradigm for achieving real performance gains with respect to existing imperative implementations, not only in comparison with uniprocessor runtimes. While the design of SAC facilitates parallelization, the particular challenge of high sequential performance is that realization of satisfying speedups through parallelization becomes substantially more difficult.

We present an initial compilation scheme and multi-threaded execution model, which we step-wise refine to reduce organizational overhead and to improve parallel performance. We close with a detailed analysis of the impact of certain design decisions on runtime performance, based on a series of experiments.

#### Contents

| 1        | Introduction                   | 2  |

|----------|--------------------------------|----|

| <b>2</b> | Arrays and array operations    | 8  |

| 3        | Generating multi-threaded code | 12 |

| 4        | With-loop scheduling           | 21 |

| 5        | Enhancing the execution model  | 25 |

| 6        | SPMD optimization              | 29 |

| 7        | Experimental evaluation        | 35 |

| 8        | Conclusion                     | 43 |

| Re       | eferences                      | 45 |

### 1 Introduction

Functional programming languages are generally considered well-suited for parallelization. Program execution is based on the principle of context-free substitution of expressions. Programs are free of side-effects and adhere to the Church-Rosser property. Any two subexpressions without data dependencies can be executed in parallel without any further analysis. Unfortunately, parallel execution inevitably incurs overhead for synchronization and communication between cooperating threads or processes. In practice, it turns out that identification of concurrent subexpressions whose parallel execution actually pays off can be almost as difficult as parallelization of imperative code (Hammond, 1994).

Numerous approaches have been developed to address this problem. In one way or another, they provide the execution machinery with hints of where and how to exploit concurrency, e.g. (Cole, 1989; Nöcker et al., 1991; Darlington et al., 1993; Bratvold, 1993; Bülck et al., 1994; Trinder et al., 1998; Trinder et al., 1999; Hammond & Portillo, 2000). Unlike annotations in imperative settings, e.g. OpenMP (Dagum & Menon, 1998), they solely affect runtime performance, but not correctness of results. Still, the goal to obtain parallel code from sequential specifications by simple recompilation is not achieved.

Other approaches provide programmers with more or less explicit means for process or thread management, synchronization, and communication, e.g. (Cooper & Morrisett, 1990; Reppy, 1991; Bailey & Newey, 1993; Jones *et al.*, 1996; Breitinger *et al.*, 1997; Kelly & Taylor, 1999; Serrarens, 1999). However, to the same extent as they provide control over parallel execution, these approaches also introduce the pitfalls of traditional parallel programming, e.g. deadlocks or race conditions.

Following their sequential host languages, all the approaches mentioned so far focus on lists or on algebraic data types in general. They are suitable tools for the parallelization of symbolic computations (Trinder et al., 1996; Loidl et al., 1999), where they benefit from the expressive power of their host languages. However, classical domains of parallel computing like image processing or computational sciences are characterized by large arrays of numerical data, not lists (Bailey et al., 1991).

Unfortunately, most functional languages are not well-suited for high-performance array processing. Notational support for multi-dimensional arrays is often rudimentary. Even worse, sequential runtime performance in terms of memory consumption and execution times fails to meet the requirements of numerical applications (Hartel & Langendoen, 1993; Hartel  $et\ al.$ , 1996; Hammes  $et\ al.$ , 1997). Their standards are set by existing implementations written and hand-optimized in low-level imperative languages like C or FORTRAN.

Parallelization is no remedy to poor sequential performance. This would require a completely implicit approach similar to a compiler optimization in addition to free availability of multiprocessor resources. In practice, however, parallelization does require additional coding, and people are usually unwilling to pay for a supercomputer only to obtain a similar runtime performance as with an imperative implementation on a uniprocessor desktop machine. At least when addressing clas-

sical domains of parallel computing, parallelization is hardly worth the effort as long as the performance of established solutions is out of reach in sequential execution.

Low sequential performance also confronts research on parallelization techniques with a specific pitfall. The ratio between time spent in synchronization/communication operations and time spent in productive code is shifted in favour of productive code. This effect makes parallelization techniques look more efficient than they actually are. The true impact of design decisions on performance is disguised, leading to false assessments.

Reasons for the poor runtime performance of general-purpose functional languages in processing multi-dimensional arrays are manifold. Certainly, all high-level language features like polymorphism, higher-order functions, partial applications, or lazy evaluation contribute some share of the overhead, but array-specific pitfalls exist as well. Conceptually, functions consume argument values and create result values from scratch. For small data items, such as list cells, this can be implemented fairly efficiently. However, operations which "change" just a few elements of a large monolithic array run into the aggregate update problem (Hudak & Bloss, 1985). They need linear time to create a copy of the whole array, whereas imperative languages accomplish the same task in constant time by destructively writing into the argument array.

Attempts to avoid or at least to mitigate this effect come at the expense of a more complex representation of arrays, which creates additional overhead elsewhere. For example, arrays could be represented as trees rather than as contiguous pieces of memory. Alternatively, "update" operations could merely be annotated internally, instead of actually being performed. While copy overhead is reduced, other array operations, e.g. element selection, become more expensive. Whether such measures improve performance or not depends on the mix of operations, but the conceptual problem remains.

Investigations involving CLEAN and HASKELL have shown that arrays need to be strict and unboxed in order to achieve acceptable runtime performance (van Groningen, 1997; Serrarens, 1997; Zörner, 1998; Chakravarty & Keller, 2003). Furthermore, array processing must be organized in a single-threaded manner, based on uniqueness types (Barendsen & Smetsers, 1995) or on state monads (Wadler, 1992). An alternative approach is taken by ID and ML. They introduce arrays as non-functional, stateful data structures. In all cases, most elegance of functional programming is lost. Arrays are allocated, copied, and removed under explicit control of the programmer.

Few functional languages have been designed with arrays in mind. Nesl (Blelloch, 1996) supports nested vectors of varying length. These sequences are half way in between lists and multi-dimensional homogeneous arrays. They are particularly useful for processing irregularly structured numerical data. A Nesl-specific optimization technique named flattening (Blelloch & Sabot, 1990) aims at increasing regularity in intermediate code in order to exploit the specific capabilities of vector processors. Investigations on runtime performance in multiprocessor environments have shown good results for applications that benefit from Nesl's support for irregularity. For example, sparse matrix operations in Nesl outperform equivalent

dense implementations in Fortran (Blelloch *et al.*, 1994). However, if data is more regularly structured and the specific capabilities of Nesl cannot be exploited, performance turns out to be inferior to Fortran.

SISAL (McGraw et al., 1985) first showed that efficient processing of regular arrays is feasible in a functional setting, provided that both language design and implementation are tailor-made. In order to reduce runtime overhead, SISAL dispenses with many typical features of functional languages. SISAL neither supports partial applications nor higher-order functions or polymorphism; the evaluation order is strict. Memory management for arrays is based on reference counting rather than on garbage collection. Hence, the exact number of active references to an array is available at runtime. Array operations can update argument arrays that are not referenced elsewhere destructively without penetrating the functional semantics (Cann, 1989). Code optimizations that exploit referential transparency (Skedzielewski & Welcome, 1985; Cann & Evripidou, 1995) and implicit generation of parallel code (Haines & Böhm, 1993) have achieved competitive performance figures for numerical benchmarks in multiprocessor environments (Oldehoeft et al., 1986; Cann, 1992).

Unfortunately, the level of abstraction in SISAL programming hardly exceeds that of imperative languages with specific array support, e.g. FORTRAN-95 (Adams et al., 1997) or ZPL (Chamberlain et al., 1998). All array operations must explicitly be specified by means of FOR-loops, a SISAL-specific array comprehension. The language neither provides built-in aggregate operations nor means to define such general abstractions. Moreover, SISAL only supports vectors. Multi-dimensional arrays must be represented as nested vectors of equal length. This limitation introduces additional indirections to array references, which incur increasing overhead with growing array rank (Scholz, 1997; Bernecky, 1997). These shortcomings are addressed in more recent versions, e.g. SISAL 2.0 (Oldehoeft, 1992) and SISAL-90 (Feo et al., 1995), but none of them have been implemented.

SAC (Single Assignment C) is a more recent functional array language (Scholz, 2003). Like Sisal, the language design of SaC aims at high runtime performance. Still, the level of abstraction in array processing considerably exceeds that of Sisal. The core syntax of SaC is a subset of C with a strict, purely functional semantics based on context-free substitution of expressions. Nevertheless, the meaning of functional SaC code coincides with the state-based semantics of literally identical C code. This design is meant to facilitate conversion to SaC for programmers with a background in imperative languages.

The language kernel of SAC is extended by multi-dimensional, stateless arrays. In contrast to other array languages, SAC provides only a very small set of built-in operations on arrays, mostly primitives to retrieve data pertaining to the structure and contents of arrays, e.g. rank, shape, or single elements. All aggregate array operations are specified in SAC itself using a versatile and powerful array comprehension construct, named with-loop. In contrast to the FOR-loops of SISAL, WITH-loops allow code to abstract not only from concrete shapes of argument arrays, but even from concrete ranks. Moreover, such rank-invariant specifications can be embedded within functions, which are applicable to arrays of any rank and shape.

By these means, most built-in operations known from FORTRAN-95 or from interpreted array languages like APL, J, or NIAL can be implemented in SAC itself without loss of generality (Grelck & Scholz, 1999). SAC provides a comprehensive selection of array operations in the standard library. Among others, the array module includes element-wise extensions of the usual arithmetic and relational operators, typical reduction operations like sum and product, various subarray selection facilities, as well as shift and rotate operations. In contrast to array support which is hard-wired into the compiler, our library-based solution is easier to maintain, to extend, and to customize for varying requirements.

SAC propagates a programming methodology based on the principles of abstraction and composition. Like in APL, complex array operations and entire application programs are constructed by composition of simpler and more general operations in multiple layers of abstractions. Unlike APL, the most basic building blocks of this hierarchy of abstractions are implemented by WITH-loops, not built-in. Whenever a basic operation is found to be missing during program development, it can easily be added to the repertoire and reused in future projects.

Despite the high-level Apl-like programming style, SAC code has managed to outperform equivalent Sisal programs (Scholz, 1999). In several case studies SAC has also proved to be competitive even with low-level, machine-oriented languages (Grelck & Scholz, 2000; Grelck, 2002; Grelck & Scholz, 2003b; Scholz, 2003; Grelck & Scholz, 2003a). We achieve this runtime behaviour by the consequent application of standard compiler optimizations in conjunction with a number of tailor-made array optimizations. They restructure code from a representation amenable to programmers and maintenance towards a representation suitable for efficient execution by machines (Scholz, 1998; Scholz, 2003; Grelck & Scholz, 2003a; Grelck et al., 2004). Both the general and the array-specific optimizations substantially benefit from the functional, side-effect free semantics of SAC.

The tailor-made language design makes SAC a suitable candidate for compiler-directed parallelization. Competitive sequential performance provides the opportunity to achieve real performance gains with respect to existing imperative implementations, not only in comparison with SAC uniprocessor runtimes. The particular challenge of high sequential performance is that realization of satisfying speedups becomes substantially more difficult. Fast sequential code is bad for the ratio between time spent in synchronization/communication operations and time spent in productive code. This ratio eventually determines parallel performance. With high sequential performance even minor inefficiencies in the organization of parallel program execution substantially degrade scalability. In this context, we have developed compilation techniques and runtime systems for the efficient parallel execution of high-level SAC array processing code on shared memory multiprocessors (Grelck, 1999; Grelck, 2001; Grelck, 2003). Our runtime system is based on the multi-threading standard Pthreads (Institute of Electrical and Electronic Engineers, Inc., 1995).

We have chosen shared memory multiprocessors as compilation target for several reasons. This increasingly popular class of machines is in wide-spread use as smalland medium-range servers. The traditional scalability bottleneck of the shared memory is mitigated by processor-specific hierarchies of large and fast caches. Larger systems actually reduce the shared memory to a shared address space on top of physically distributed memory and a highly integrated interconnection network (Hennessy & Patterson, 2003). The Top500 list of the most powerful computing sites worldwide (Dongarra *et al.*, 2003) demonstrates the suitability of shared memory systems for complex computational tasks in practice.

Since SAC is a dedicated array language, typical SAC code is dominated by array operations. In one way or another all aggregate array operations in SAC are implemented by WITH-loops. Hence, WITH-loops form the ideal basis for parallelization, following a data parallel approach. Targeting shared memory architectures in general and PTHREADS in particular makes explicit decomposition of arrays and data exchange via message passing superfluous. Hence, integral parts of the existing sequential compiler framework can be reused with only minor alterations. Therefore, we can concentrate all effort on those aspects of the compilation process that are specific to multi-threaded execution.

Our initial compilation scheme focuses on the efficient parallel execution of individual WITH-loops. This leads to a *fork-join* execution model. A *master thread* executes a program just as in the sequential case. As soon as it reaches a WITH-loop, the master thread creates a fixed number of *worker threads*. The worker threads cooperatively compute the WITH-loop and terminate. Meanwhile, the master thread waits for the last worker thread to complete its share of work and resumes sequential execution thereafter.

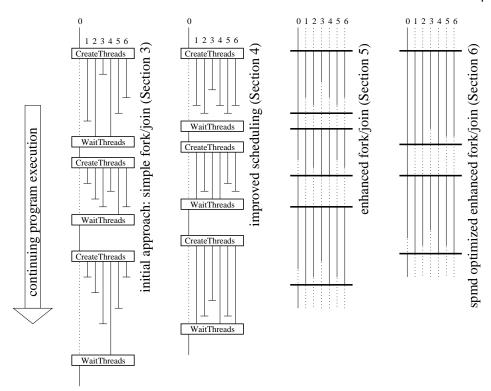

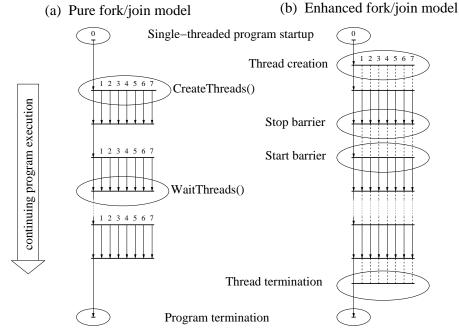

The organization of multi-threaded program execution inevitably incurs some overhead. In order to achieve high parallel performance and reasonable scalability we must address all sources of overhead and try to avoid or to reduce them as far as possible. In our initial approach we can identify various sources of overhead: creation and termination of threads or synchronization and communication between threads. Moreover, program execution frequently stalls at barriers. These sources of overhead are addressed by a step-wise refinement of the initial compilation scheme and execution model. Fig. 1 illustrates the refinement steps starting with the initial approach on the left hand side. Vertical lines represent threads computing over time. Dotted lines refer to sleeping threads. Horizontal boxes and bars represent synchronization and communication. The master thread has thread ID 0; the example uses 6 worker threads.

Our initial approach is characterized by a sequence of parallel execution steps interrupted by sequential phases. As a first refinement step, we investigate various WITH-loop scheduling techniques. WITH-loop scheduling is the process of partitioning WITH-loop among worker threads for execution. Different approaches are developed that aim at a smooth distribution of workload, without ignoring such important issues as scheduling overhead or data locality. In Fig. 1, this is indicated by adjusting the length of lines which represent computing threads.

In a second step, the initial fork/join execution model is refined to an enhanced fork/join model. Worker threads remain alive during the whole program execution. Costly thread creation and thread termination operations are replaced by tailor-made synchronization barriers. They aim at reducing the runtime overhead directly

Fig. 1: Illustration of the refinement of compilation schemes and multi-threaded execution models from the initial approach (left) to the final solution (right).

inflicted by synchronization and communication. In Fig. 1, this is indicated by replacing horizontal boxes by thin bars. Moreover, the master thread participates in the cooperative execution of WITH-loops by temporarily turning itself into a worker thread rather than sleeping until completion of the WITH-loop.

In the third refinement step, regions of parallel activity are decoupled from individual WITH-loops. We introduce explicit skeleton-like intermediate language constructs for the internal representation of synchronization and communication patterns. Tailor-made optimization schemes aim at fusing subsequent steps of parallel execution into single ones. On the right hand side of Fig. 1, this is illustrated by fusing the first and the second parallel section. This step reduces the number of synchronization barriers and creates larger regions of parallel execution, which also render scheduling techniques for workload distribution more effective.

The three refinement steps are presented in the order they have been developed. In fact, they are mostly independent of each other. Since they address different sources of overhead in different ways, they could be applied in any order. Still, all three refinement steps substantially benefit from each other. Only in conjunction they achieve the desired runtime performance in parallel execution.

The remainder of the paper gives a comprehensive and detailed presentation and evaluation of the compilation techniques sketched out above. Section 2 introduces the array concept of SAC in general and the WITH-loop in particular. Section 3

elaborates on the compilation of individual WITH-loops into multi-threaded code. Various WITH-loop scheduling techniques are discussed in Section 4. Section 5 refines the initial execution model towards the enhanced fork/join model. Section 6 describes the introduction of skeleton-like structures for the internal representation of synchronization and communication patterns and the fusion of multiple regions of parallel execution. Section 7 summarizes various experiments that investigate the suitability of the approach in general and the effectiveness of individual measures in particular. Section 8 draws conclusions.

### 2 Arrays and array operations

Arrays in SAC are represented by two vectors. The *shape vector* specifies an array's rank (number of axes or number of dimensions) and the number of elements along each axis. The *data vector* contains all elements of an array in row-major order. Their relationship is defined as follows. Let A be an n-dimensional array represented by the shape vector  $\vec{s}_A = [s_0, \ldots, s_{n-1}]$  and by the data vector  $\vec{d}_A = [d_0, \ldots, d_{m-1}]$ . Then the equation

$$m = \prod_{i=0}^{n-1} s_i$$

describes the correspondence between the shape vector and the length of the data vector. Moreover, the set of legal index vectors of the array A is defined as

$$\mathcal{IV}_A := \{ [iv_0, \dots, iv_{n-1}] \mid \forall j \in \{0, \dots, n-1\} : 0 \leq iv_j < s_j \} .$$

An index vector  $\vec{iv} = [iv_0, \dots, iv_{n-1}]$  denotes the element  $d_k$  of the data vector  $\vec{d}_A$  of array A if  $\vec{iv}$  is a legal index vector of A, i.e.  $\vec{iv} \in \mathcal{IV}_A$ , and the equation

$$k = \sum_{i=0}^{n-1} (iv_i * \prod_{j=i+1}^{n-1} s_j)$$

holds. For example, the matrix

$$\begin{pmatrix} 0 & 1 & 2 & 3 & 4 & 5 & 6 & 7 & 8 & 9 \\ 10 & 11 & 12 & 13 & 14 & 15 & 16 & 17 & 18 & 19 \\ 20 & 21 & 22 & 23 & 24 & 25 & 26 & 27 & 28 & 29 \\ 30 & 31 & 32 & 33 & 34 & 35 & 36 & 37 & 38 & 39 \\ 40 & 41 & 42 & 43 & 44 & 45 & 46 & 47 & 48 & 49 \end{pmatrix}$$

is represented by the shape vector [5,10] and the data vector

$$[0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, \dots, 47, 48, 49]$$

The set of legal index vectors is

$$\{[i,j] \mid [0,0] \leq [i,j] < [5,10] \}$$

and the index vector [3,2] refers to element position 32 of the data vector.

As pointed out in the introduction, SAC provides only a very small set of built-in operations on arrays, mostly primitives to retrieve data pertaining to the structure

and contents of arrays. For example, shape(a) and dim(a) yield the shape and the rank of an array a, respectively. Furthermore, sel(iv, a) yields the element of a at index position iv, provided that the length of the integer vector iv matches the rank of the array a. Applications of the form sel(iv, a) may be replaced by the more familiar notation a[iv].

# With-loops

All aggregate array operations are specified in SaC itself using a versatile and powerful array comprehension construct, named with-loop. WITH-loops are versatile language constructs for the specification of potentially complex map- and fold-like aggregate array operations. A definition of their syntax is given in Fig. 2. Following the key word with, a WITH-loop is made up of a non-empty sequence of parts and a single operation. The operation determines the overall meaning of the WITH-loop. There are two variants: genarray and fold. With genarray (Expr) the WITH-loop creates a new array. The expression Expr must evaluate to an integer vector, which defines the shape of the array to be created. With fold (FoldOp, Expr) the WITH-loop specifies a reduction operation. In this case, FoldOp must be the name of an appropriate associative and commutative binary operation. The expression Expr must evaluate to the neutral element of FoldOp.

```

WithLoopExpr \Rightarrow with [Part]^+ Operation

Part \Rightarrow (Generator) : Expr

Generator \Rightarrow Expr \Leftarrow Identifier \Leftarrow Expr [Filter]

Filter \Rightarrow step Expr [width Expr]

Operation \Rightarrow genarray (Expr)

fold (FoldOp, Expr)

Fig. 2: Syntax definition of WITH-loops.

```

Each part consists of a *generator* and an expression. The expression is said to be associated with the generator. The generator defines a set of index vectors along with an *index variable* representing elements of this set. Two expressions, which must evaluate to non-negative integer vectors of equal length, define lower and upper bounds of a rectangular range of index vectors. For each element of the index vector set defined by a generator, the associated expression is evaluated. Depending on the operational variant of the WITH-loop, the value of the associated expression either defines the element value at the corresponding index position of the new array (genarray), or it is given as an argument to the fold operation (fold).

yields

For example, the matrix

$$\begin{pmatrix} 0 & 1 & 2 & 3 & 4 & 5 & 6 & 7 & 8 & 9 \\ 10 & 11 & 12 & 13 & 14 & 15 & 16 & 17 & 18 & 19 \\ 20 & 21 & 22 & 23 & 24 & 25 & 26 & 27 & 28 & 29 \\ 30 & 31 & 32 & 33 & 34 & 35 & 36 & 37 & 38 & 39 \\ 40 & 41 & 42 & 43 & 44 & 45 & 46 & 47 & 48 & 49 \end{pmatrix}$$

may be specified by the following WITH-loop:

```

with

([0,0] <= iv < [5,10]) : iv[0] * 10 + iv[1]

genarray( [5,10])

Similarly,

with

([0,0] <= iv < [5,10]) : iv[0] * 10 + iv[1]

fold( +, 0)</pre>

```

computes the sum of all elements of the example matrix without actually creating the matrix.

With multiple parts, disjoint index subsets of an array may be computed and initialized according to different specifications. For example,

```

with

([0,0] <= iv < [5, 8]) : iv[0] * 10 + iv[1]

([0,8] <= iv < [5,10]) : 0

genarray( [5,10])

yields</pre>

```

$$\begin{pmatrix} 0 & 1 & 2 & 3 & 4 & 5 & 6 & 7 & 0 & 0 \\ 10 & 11 & 12 & 13 & 14 & 15 & 16 & 17 & 0 & 0 \\ 20 & 21 & 22 & 23 & 24 & 25 & 26 & 27 & 0 & 0 \\ 30 & 31 & 32 & 33 & 34 & 35 & 36 & 37 & 0 & 0 \\ 40 & 41 & 42 & 43 & 44 & 45 & 46 & 47 & 0 & 0 \end{pmatrix}$$

An optional filter may be used to restrict index sets to grids. For example,

```

with

([0,0] <= iv < [5,10] step [1,2]) : iv[0] * 10 + iv[1]

([0,1] <= iv < [5,10] step [1,2]) : 0

genarray( [5,10])</pre>

```

$\begin{pmatrix} 0 & 0 & 2 & 0 & 4 & 0 & 6 & 0 & 8 & 0 \\ 10 & 0 & 12 & 0 & 14 & 0 & 16 & 0 & 18 & 0 \\ 20 & 0 & 22 & 0 & 24 & 0 & 26 & 0 & 28 & 0 \\ 30 & 0 & 32 & 0 & 34 & 0 & 36 & 0 & 38 & 0 \\ 40 & 0 & 42 & 0 & 44 & 0 & 46 & 0 & 48 & 0 \end{pmatrix}$

An additional width specification allows generators to define generalized grids as in the following example where

```

with

([0,0] <= iv < [5,10] step [4,4] width [2,2]) : 9

([0,2] <= iv < [5,10] step [4,4] width [2,2]) : 0

([2,0] <= iv < [5,10] step [4,1] width [2,1]) : 1

genarray( [5,10])</pre>

```

vields

Expressions that define step and width vectors must evaluate to positive integer vectors of the same length as the bound vectors of the generator. The full range of generators can also be used with fold-WITH-loops.

In order to give a formal definition of index sets, let a, b, s, and w denote expressions that evaluate to appropriate vectors of length n. Then the generator

(

$$a \le iv \le b \text{ step } s \text{ width } w$$

)

defines the following set of index vectors:

$$\{ iv \mid \forall j \in \{0, ..., n-1\} : a_i \leq iv_i < b_i \land (iv_i - a_i) \mod s_i < w_i \}$$

.

Two constraints which cannot be expressed by means of syntax apply to WITH-loops. Firstly, the index sets defined by multiple generators must be pairwise disjoint. Secondly, for genarray-WITH-loops the union of all index sets must equal the set of legal index vectors of the result array, i.e., each element of the result array must be associated with exactly one generator.

An important property of WITH-loops is that evaluation of the associated expression for any element of the union of index sets is completely independent of all others, leaving a language implementation free to choose any suitable evaluation order. We exploit this property both for optimization and for parallelization. Consequently, WITH-loops form the basis for large-scale code restructuring optimizations, which combine several individual WITH-loops into a single one. Therefore, the average computational workload per array element is much higher than for the mostly light-weight built-in aggregate operations in other languages. Since increased workload per element generally improves the ratio between productive computations and runtime overhead, WITH-loops are particularly amenable to parallel execution.

Unfortunately, the various benefits of WITH-loops do not come for free. Whereas built-in array operations in other languages are almost always homogeneous, WITH-loops may represent considerably inhomogeneous operations. A single WITH-loop may consist of many generators defining disjoint, but potentially interleaved, index vector sets. Moreover, associated expressions may substantially differ from each other with respect to their computational complexity. Such inhomogeneities significantly complicate the generation of efficiently executable code.

In a sense, WITH-loops resemble algorithmic skeletons (Cole, 1989; Cole, 2004)

liberated from restrictions imposed by their typical realization as higher-order functions in statically typed languages. Actually, <code>genarray-WITH-loops</code> are powerful array comprehensions, and <code>fold-WITH-loops</code> are versatile folding templates, both specifically designed for multi-dimensional arrays. By their semantics, they explicitly introduce fine-grained concurrency into SAC programs in a way that is particularly amenable to exploitation for parallel execution. Whether some WITH-loop actually is executed in parallel by multiple processors or sequentially by a single processor, is solely up to compiler and runtime system. Even within a single compiled code, the same WITH-loop may be executed in parallel sometimes and sequentially otherwise, depending on the state of the execution machinery. WITH-loops do not specify a pattern of parallel behaviour, but — in conjunction with the entire language design of SAC — they facilitate automatic or implicit parallelization.

## 3 Generating multi-threaded code

When contemplating the multi-threaded execution of SAC programs, it turns out that some program parts require sequential execution by a dedicated thread. For example, I/O operations must be performed in a single-threaded way in order to preserve the sequential I/O behaviour. I/O operations and state modifications in general are properly integrated into the purely functional world of SAC by a variant of uniqueness types (Achten & Plasmeijer, 1995), named *classes* (Grelck & Scholz, 1995). Enforcing the uniqueness property bans all state modifications from bodies of WITH-loops. Hence, the easiest way to preserve sequential I/O behaviour is to restrict parallel program execution to individual WITH-loops.

Following this idea, a master thread executes most parts of a SAC program in a single-threaded way, similar to sequential execution. Only when it comes to computing a WITH-loop, the master thread creates the desired number of additional worker threads. Subsequently, all worker threads concurrently, but cooperatively, execute the single WITH-loop. Meanwhile, the master thread merely awaits the termination of the worker threads. After all worker threads have finished their individual shares of work, they terminate, and the master thread resumes sequential execution.

The PTHREADS standard does not provide any means to associate threads with processors. The host machine's operating system is responsible for scheduling worker threads to different processors in a reasonable way. In general, it is recommended to use exactly one thread per processor. This choice avoids frequent context switches between cooperating threads and proved optimal in extensive experiments.

In the following, we present detailed schemes for compiling individual WITH-loops into multi-threaded code. Our initial focus is on genarray-WITH-loops; fold-WITH-loops are covered towards the end of this section. Rules of the form

$$\mathcal{C}[[expr]] = expr'$$

denote the context-free replacement of a SAC program fragment expr by a pseudo C program fragment expr'.

## Compilation of genarray-with-loops

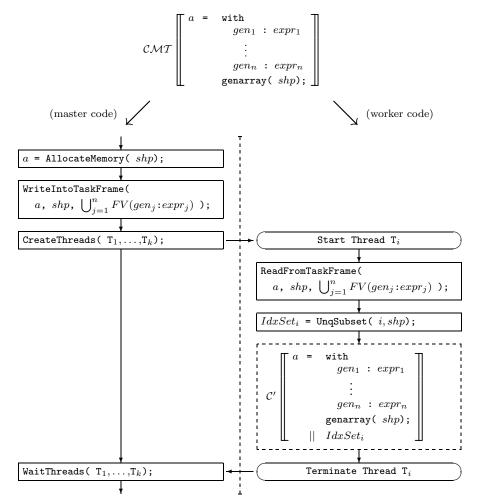

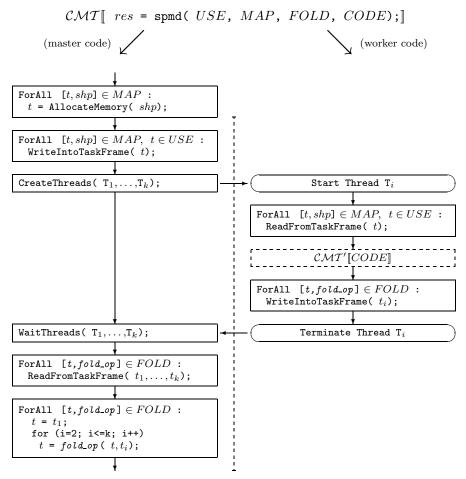

Fig. 3 shows the compilation scheme  $\mathcal{CMT}$  for generating multi-threaded C code from a single genarray-WITH-loop. Actually, two different fragments of C code are generated: one for the master thread and one for the worker threads. Their interaction is indicated by horizontal arrows.

Fig. 3: Multi-threaded compilation scheme for genarray-WITH-loops.

Whenever execution of the master thread reaches a genarray-WITH-loop, it first allocates memory appropriate for storing the result array. Here and in the sequel, we assume that nested expressions have already been flattened by a pre-processing step. Hence, *shp* denotes a variable referring to the shape of the array to be created rather than a complex expression. Due to the commitment to shared memory architectures, explicit decomposition of arrays is obsolete. Hence, implicit dynamic memory management for arrays can be adopted from the existing sequential implementation with only minor adaptations. Arrays are still stored in a single contiguous

address space. Memory is allocated by the master thread during single-threaded execution.

For worker threads to be able to compute their individual shares of a WITHloop, it is necessary to set up an execution environment equivalent to that of the master thread. More precisely, all those variables referred to within the body of the WITH-loop, but defined before, must also exist in the worker thread. Moreover, they must be initialized to the current values in the master thread to ensure proper execution of the WITH-loop by each worker thread. The required information must be communicated to the worker threads before they start execution of productive code. In a shared memory environment communication is realized by writing to and reading from global data structures. Therefore, each WITH-loop in a SAC program is associated with a global buffer, called task frame. The task frame is tailor-made for communication between master thread and worker threads for that individual WITH-loop. In the case of a genarray-WITH-loop, the master thread — in addition to the values of all free variables of the various generator-expression pairs — stores the pre-allocated result array and its shape in the task frame. Due to the shared memory, it suffices to communicate the base addresses and the shapes of arrays, rather than the arrays themselves.

Eventually, the desired number of worker threads is created. The actual number may either be fixed at compile time, or it is determined by a command line parameter or by an environment variable upon program start. In any case, the number of threads remains constant throughout an entire program run.

All worker threads uniformly execute the code shown on the right hand side of Fig. 3, but each thread may identify itself by means of a unique ID. As a first step, a worker thread sets up its execution environment by extracting the required information from the task frame. Access to the task frame can always be granted without costly synchronization of threads via critical regions or similar. As long as the master thread writes to the task frame, it is known to be the only thread in the process. As soon as multiple threads exist, the task frame is used as a read-only buffer.

Although all worker threads execute exactly the same code, they must compute and initialize pairwise disjoint sets of result array elements for parallel execution to make sense. This additional side condition must be taken into account when eventually compiling a WITH-loop into nestings of FOR-loops in C. Even in the sequential case, generation of efficient code from WITH-loops with multiple interleaved generators has proved to be an extremely complicated and challenging task (Grelck et al., 2000; Scholz, 2003). Therefore, we want to reuse the existing sequential code generation scheme for WITH-loops as far as possible. However, we need to associate each element of the result array with exactly one thread. The scheduling of array elements to threads directly affects workload distribution among processors and is vital for performance.

The solution adopted in Fig. 3 keeps code generation and scheduling as separate as possible. By means of the runtime system function UnqSubset each worker thread determines a rectangular index subspace  $IdxSet_i$  based on its unique ID and the shape of the result array. Proper implementations of UnqSubset guarantee that

each legal index position of the result array is covered by exactly one such index subspace. Different implementations of UnqSubset allow us to realize various different scheduling techniques without affecting the compilation scheme otherwise. Based on programmer annotations or on compiler heuristics, the most appropriate scheduler implementation may be selected. Section 4 further elaborates on this topic.

After initialization of the execution environment and allocation of a rectangular index subspace by the loop scheduler, execution of the WITH-loop by an individual worker thread proceeds almost as in the sequential case. In Fig. 3, this is indicated by the recursive application of the code generation scheme  $\mathcal{C}'$ , which is a variant of the sequential code generation scheme  $\mathcal{C}$  (Scholz, 2003). The most significant difference between  $\mathcal{C}'$  and  $\mathcal{C}$  is that the range of any FOR-loop in compiled code is restricted to the intersection of its original range and the rectangular index subspace  $IdxSet_i$  allocated by the WITH-loop scheduler. After having completed its individual share of work, a worker thread terminates. The master thread waits for the longest-running worker thread to terminate and resumes sequential execution.

# Code generation for worker threads

The adapted code generation scheme  $\mathcal{C}'$  for worker threads is formally defined in Fig. 4. The code starts by allocating memory to accommodate the index variable iv. Afterwards, the compilation scheme  $\mathcal{C}'$  is recursively applied to each part of the multi-generator WITH-loop individually. The specification of the local index subspace IdxSet is propagated as is. However, this is not done before the corresponding expressions to be evaluated are transformed into assignments of the form  $a[iv] = \mathcal{C}[expr]$ , which ensures correct insertion of the computed values into the result array. Using the compilation scheme  $\mathcal{C}$  here instead of  $\mathcal{C}'$  reflects the fact that compilation of these expressions is independent of the choice of sequential

```

C' \begin{bmatrix} a = \text{with} & (l_1 \le iv \le u_1 \text{ step } s_1 \text{ width } w_1 ) : expr_1 \\ \vdots & (l_n \le iv \le u_n \text{ step } s_n \text{ width } w_n ) : expr_n \\ \text{genarray}(shp); \\ \parallel IdxSet \end{bmatrix}

= \begin{cases} iv = \text{AllocateMemory}(\text{ shape}(l_1)); \\ C' \begin{bmatrix} (l_1 \le iv \le u_1 \text{ step } s_1 \text{ width } w_1 ) : a[iv] = C[expr_1]; \\ \parallel IdxSet \end{bmatrix}

\vdots \\ C' \begin{bmatrix} (l_n \le iv \le u_n \text{ step } s_n \text{ width } w_n ) : a[iv] = C[expr_n]; \\ \parallel IdxSet \end{bmatrix}

FreeMemory(iv);

Fig. 4: Code generation scheme for genarray-WITH-loops.

```

or multi-threaded program execution. Finally, we de-allocate the memory holding the index variable because the index variable's scope is always confined to a single WITH-loop.

```

C' \begin{bmatrix} ([l_i, \dots, l_{m-1}] <= iv < [u_i, \dots, u_{m-1}] \\ \text{step } [s_i, \dots, s_{m-1}] \text{ width } [1, w_{i+1}, \dots, w_{m-1}]) : Assign \\ \| [lb_i, \dots, lb_{m-1}] [ub_i, \dots, ub_{m-1}] \end{bmatrix} \\ = \begin{cases} \text{for } (iv[i] = \max(\ l_i, \ lb_i); \ iv[i] < \min(\ u_i, \ ub_i); \ iv[i] += s_i) \ \{ \\ C' \begin{bmatrix} ([l_{i+1}, \dots, l_{m-1}] <= iv < [u_{i+1}, \dots, u_{m-1}] \\ \text{step } [s_{i+1}, \dots, s_{m-1}] \ \text{width } [w_{i+1}, \dots, w_{m-1}] \ ) : Assign \\ \| [lb_{i+1}, \dots, lb_{m-1}] [ub_{i+1}, \dots, ub_{m-1}] \end{bmatrix} \\ C' \begin{bmatrix} ([l_i, \dots, l_{m-1}] <= iv < [u_i, \dots, u_{m-1}] \\ \text{step } [s_i, \dots, s_{m-1}] \ \text{width } [w_i, \dots, w_{m-1}] \ ) : Assign \\ \| [lb_i, \dots, lb_{m-1}] [ub_i, \dots, ub_{m-1}] \end{bmatrix} \\ = \begin{cases} \text{for } (iv[i] = \max(\ l_i, \ lb_i); \ iv[i] < \min(\ u_i, \ ub_i); \ iv[i] += s_i - w_i) \ \{ \\ \text{stop } = \min(\ iv[i] + w_i, \ \min(\ u_i, \ ub_i)); \ \text{for } (\ ; iv[i] < \text{stop}; \ iv[i] += 1) \ \{ \\ C' \begin{bmatrix} ([l_{i+1}, \dots, l_{m-1}] <= iv < [u_{i+1}, \dots, u_{m-1}] \\ \text{step } [s_{i+1}, \dots, s_{m-1}] \ \text{width } [w_{i+1}, \dots, w_{m-1}] \ ) : Assign \end{bmatrix} \\ = \begin{cases} C' [(\ [] <= \text{iv} < [\ ] \text{ step } [\ ] \text{ width } [\ ] \ ) : Assign \ \| [\ ] \ [\ ] \ ] = Assign \end{cases} \end{cases}

```

Fig. 5: Code generation scheme for individual parts.

Generation of C FOR-loops for individual parts of a WITH-loop is defined in Fig. 5. The compilation scheme  $\mathcal{C}'$  generates either one or two FOR-loops for each dimension or axis of the index space. If the corresponding element of the width vector is known to evaluate to one, the scheme generates a single FOR-loop only. It runs on the intersection between the range defined by lower and upper bound of the generator,  $\vec{l}$  and  $\vec{u}$ , and the local index subspace, which itself is defined by the lower and upper bound vectors  $\vec{l}\vec{b}$  and  $\vec{u}\vec{b}$ . The corresponding step vector component determines the FOR-loop's increment.

If the current component of the width vector differs from one or is unknown at compile time, we must create two nested FOR-loops: an outer loop for initialization and stepwise increment of the corresponding index variable component and an inner loop for realization of the width component. The body of the inner loop is derived from recursive application of the code generation scheme  $\mathcal{C}'$  with the leading elements of the four generator vectors removed. The innermost loop body is defined by the pregenerated assignment, which is specific to the WITH-loop variant.

As pointed out before, one important property of WITH-loops is the freedom to choose any suitable evaluation order. We prominently exploit this property for compilation into multi-threaded code. In a less obvious way, the property is also exploited by the code generation scheme  $\mathcal{C}'$ , as defined in Fig. 4 and in Fig. 5. Addressing each generator of a multi-generator WITH-loop in isolation substantially facilitates the compilation process. Unfortunately, this straightforward approach has two major disadvantages with respect to achieving high runtime performance.

- Separate compilation of generators introduces a considerable amount of loop overhead, in particular if step and width vectors are used.

- Cache memory utilization is poor because data transfer between main memory and cache memory in whole cache lines favours consecutive memory references to adjacent addresses (Hennessy & Patterson, 2003).

Although elaborate C compilers provide optimizations for rearranging loops (Zima & Chapman, 1991; Wolfe, 1995; Allen & Kennedy, 2001), they usually fail to improve compiled SAC code in a substantial way because they lack information about the special properties of the code. For example, C compilers do not a-priori know that all innermost loop bodies can be computed independently of each other or that each result array element is initialized exactly once. Instead, this information must be inferred from the code, which proves to be quite difficult in the context of C. C compilers hardly achieve the required accuracy and must make conservative assumptions.

To overcome these limitations, the sequential code generation scheme  $\mathcal{C}$  is extended by a post-processing phase, which systematically transforms generator-centric nestings of FOR-loops into equivalent ones that obey the *canonical order* (Grelck *et al.*, 2000). Elements of the result array are computed and initialized in strictly ascending order according to the array's memory representation. The canonical order overcomes both deficiencies of the initial approach, excessive loop overhead and poor cache utilization. This post-processing phase has turned out to be crucial for overall performance. Fortunately, the design of the compilation scheme  $\mathcal{CMT}$  allows us to reuse the sequential post-processing phase for worker thread code without modification. Therefore, we omit a detailed description here and refer to (Grelck *et al.*, 2000) and (Scholz, 2003) for additional information.

# Compilation of fold-with-loops

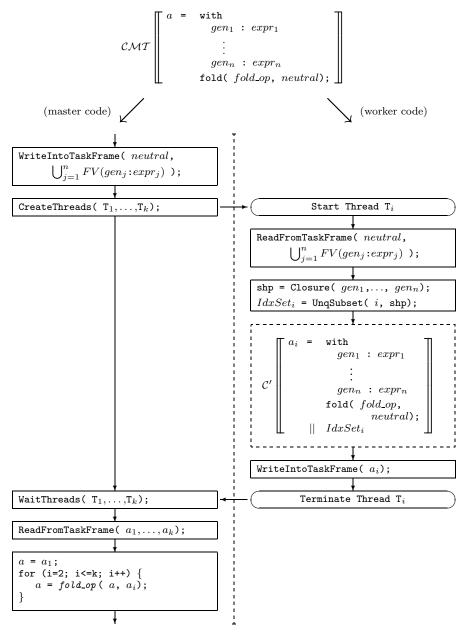

Fig. 6 shows the generation of multi-threaded code for fold-WITH-loops. Worker threads initialize a local accumulation variable  $a_i$  by the neutral element of the fold operation. Each worker thread computes a partial fold result based on a subset of the values to be folded. Upon termination of the worker threads, the master thread collects their partial fold results and computes the overall result. Unlike some notions of fold skeletons, e.g. as described in (Michaelson *et al.*, 2001), parallel activity unfolds and resumes all at once rather than in a divide-and-conquer style.

Compiled code for the master thread starts by writing the values of the WITH-loop body's free variables into the corresponding task frame. The same happens to the fold operation's neutral element. Analogously to the result array shape shp in the compilation of <code>genarray-WITH-loops</code>, we assume neutral to refer to a simple vari-

Fig. 6: Multi-threaded compilation scheme for fold-WITH-loops.

able. Having set up the task frame, the master thread creates the desired number of worker threads. Worker threads set up their execution environment, retrieved from the task frame. After that, each worker thread identifies a unique index subspace by calling the loop scheduler UnqSubset. However, the loop scheduler requires the shape of the overall index space as an argument. In contrast to genarray-WITH-loops, this information is not immediately available in fold-WITH-loops. Instead,

it must be determined from the set of generators. In Fig. 6, this is expressed by the pseudo operation Closure, which yields the smallest rectangular hull of the transitive closure of the generators.

Recursive application of the adapted code generation scheme C' to the WITH-loop itself and the description of the unique index subspace  $IdxSet_i$  results in code that computes a partial fold result, which is stored in the (thread-) local accumulation variable  $\mathbf{a}_i$ . Upon completion, a worker thread writes its partial fold result into the task frame and terminates. In order to avoid costly synchronization upon concurrent access to the task frame by worker threads, the task frame provides a dedicated entry for each worker thread. The master thread awaits termination of all worker threads before it extracts the partial fold results from the task frame. Finally, the master thread itself combines the various partial fold results to generate the overall result and resumes sequential execution.

```

C' \begin{bmatrix} a = \text{with} & (l_1 <= iv < u_1 \text{ step } s_1 \text{ width } w_1 \text{ }) : expr_1 \\ \vdots & \vdots & (l_n <= iv < u_n \text{ step } s_n \text{ width } w_n \text{ }) : expr_n \\ \text{fold(} fold\_op, neutral); \\ || IdxSet \end{bmatrix}

= \begin{cases} a = neutral; \\ iv = \text{AllocateMemory( shape(} l_1)\text{)}; \\ C' \begin{bmatrix} (l_1 <= iv < u_1 \text{ step } s_1 \text{ width } w_1 \text{ }) : a = fold\_op( a, C[expr_1]); \\ || IdxSet \end{bmatrix} \\ \vdots \\ C' \begin{bmatrix} (l_n <= iv < u_n \text{ step } s_n \text{ width } w_n \text{ }) : a = fold\_op( a, C[expr_n]); \\ || IdxSet \end{bmatrix}

FreeMemory( iv);

Fig. 7: Code generation scheme for fold-WITH-loops.

```

Fig. 7 shows the definition of the adapted code generation scheme  $\mathcal{C}'$  for fold-WITH-loops. First, a worker thread initializes a local accumulation variable **a** by the neutral element of the fold operation and allocates memory for the index variable iv. After that, the compilation scheme  $\mathcal{C}'$  is recursively applied to each generator with the fold operation pregenerated. By abstracting from the actual operation to be inserted into the innermost FOR-loop body, the loop generation scheme defined in Fig. 5 can be reused for fold-WITH-loops without modification.

## Nested with-loops

Raising the focus from compilation intricacies of individual WITH-loops to the execution of entire programs, it becomes clear that program execution always is in one of two states. Either WITH-loops are evaluated by a fixed number of worker threads in

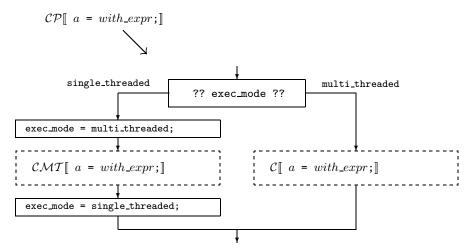

parallel, or some other code is executed sequentially by the master thread. However, WITH-loops may be nested, both statically in the code or dynamically in the unfolding of program execution. Program execution may already be in multi-threaded mode when it reaches a WITH-loop again. Since the number of threads already equals the number of available processors, we must prevent a recursive unfolding of parallel activity. WITH-loops that are nested within others, either statically or dynamically, must be executed sequentially. This is achieved by embedding the compilation scheme  $\mathcal{CMT}$  within a more general scheme  $\mathcal{CP}$ , as shown in Fig. 8.

Fig. 8: Generalized compilation scheme  $\mathcal{CP}$ .

The runtime system maintains a global flag exec\_mode, which keeps track of the current state of program execution. Whenever program execution encounters a WITH-loop, the value of the exec\_mode flag is inspected. Depending on its state, program execution either branches into multi-threaded code (generated by the compilation scheme  $\mathcal{CMT}$ ) or into sequential code (generated by the compilation scheme  $\mathcal{C}$ ). In the former case, the exec\_mode flag is inverted during execution of the multi-threaded code. Access to the global state flag goes without protection because any write operation on it is guaranteed to be executed by the master thread while it is the only thread of the process. Inspection of the exec\_mode flag can be avoided for statically nested WITH-loops. Moreover, simple heuristics identify WITH-loops for which parallel execution is likely not to pay off.

Although the compilation scheme  $\mathcal{CP}$  restricts the unfolding of parallel activity to a single level, this does not mean sequential execution of all WITH-loops that are nested within others. A SAC-specific optimization technique named WITH-LOOP-SCALARIZATION (Grelck  $et\ al.$ , 2004) aims at transforming static nestings of WITH-loops into single ones — regardless of whether code is compiled for multi-threaded or for sequential execution. In any case, it is reasonable to assume that an outermost WITH-loop provides sufficiently fine-grained concurrency to exploit all available processors. This is an advantage of processing homogeneous arrays in-

stead of lists or trees. Moreover, in shared memory environments processor counts are limited by the trade-off between scalability and hardware cost. Dispensing with nested levels of parallelism, the entire problem space discussed in the context of nested algorithmic skeletons (see for example (Hamdan *et al.*, 1999; Michaelson *et al.*, 2001)) can be avoided. As a consequence, our runtime system is significantly more efficient for realistic applications. This can be observed when comparing SAC performance figures with, for example, those in (Hamdan *et al.*, 1999; Michaelson *et al.*, 2001).

# 4 With-loop scheduling

WITH-loop scheduling is the process of allocating each element of the global index space defined by a WITH-loop to exactly one worker thread. This worker thread is then responsible for evaluation of the associated expression and for initialization of the corresponding element of the result array (genarray-WITH-loop) or for execution of the folding operation (fold-WITH-loop). Conceptually, each element of the global index set could be processed in parallel by a different thread. However, the useful number of threads is limited by the number of available processors. Typically, the size of the global index set by far exceeds the number of worker threads. Therefore, it is necessary to allocate entire index subspaces to worker threads rather than individual elements of the global index set. To facilitate compilation into efficiently executable code, the compilation schemes outlined in the previous section only support dense rectangular index subspaces. Similar to WITH-loop generators, they are represented by two boundary vectors.

In addition to these technical requirements, the main task of WITH-loop scheduling is to distribute the computational workload among threads as evenly as possible. Since the parallel execution of a WITH-loop is completed by a barrier synchronization, overall execution time is determined by the "slowest" thread. Successful workload balancing is one major prerequisite for achieving good parallel performance. Unfortunately, the process of finding a suitable workload distribution contributes to organizational overhead. Hence, the scheduling problem is characterized by a trade-off between quality of workload balancing and overhead produced. Since the scheduling problem itself is not SAC-specific, we summarize existing approaches first and describe the solution adopted for the specific conditions of our compilation framework towards the end of the section.

## Static scheduling

Two classes of loop scheduling techniques can be distinguished: *static* and *dynamic* approaches. Static techniques employ an a-priori association of loop iterations with threads. Well-known representatives of this class are *block* scheduling, *cyclic* scheduling, and *block-cyclic* scheduling. They are illustrated in Fig. 9 for the 2-dimensional case and four threads. Block scheduling subdivides the iteration space into disjoint rectangular blocks, one for each thread. Cyclic scheduling associates every *n*-th iteration with the same thread. As a combination of both, block-cyclic

Fig. 9: Examples of static scheduling schemes.

scheduling subdivides the iteration space into blocks of a fixed size and applies cyclic scheduling on the level of these blocks. In the context of multi-dimensional loops or loop nestings, additional degrees of freedom arise from the selection of one or several scheduling dimensions and the possibility to combine different techniques along different axes of the iteration space.

Static scheduling techniques have been studied intensively in the context of HPF and its predecessors (Tseng, 1993; Loveman, 1993; Koebel et al., 1994; Roth, 1997). If the computational workload is regularly distributed over the iteration space, block scheduling combines low overhead with good workload balancing and high data locality. Cyclic scheduling is the choice whenever workload depends on the loop index, e.g. when processing triangular matrices. However, on modern cachebased computer architectures cyclic scheduling suffers from poor data locality. It is usually replaced by block-cyclic scheduling, which often is a reasonable compromise between data locality and workload balancing.

## Dynamic scheduling

Multiprocessor systems rarely run a single application only. Threads of compiled SAC code compete for limited computing resources with unrelated processes incidentally running on the same system. As a matter of principle, static scheduling techniques cannot reflect changing workload characteristics of machines which run several independent processes. This scenario asks for *dynamic* or *adaptive* scheduling techniques.

Early examples such as *self-scheduling* (Tang & Yew, 1986) or *uniform-sized chunking* (Kruskal & Weiss, 1985) associate individual iterations or entire sets of iterations to threads on demand. A central task queue stores tasks ready to be

computed. Each thread retrieves a new task from the task queue as soon as it has finished its previous task. This technique ensures proper balancing even in the presence of irregular workload distributions and changing availability of processors. Unfortunately, this advantage comes at the expense of considerable organizational overhead for managing the central task queue. Shared among all threads, the task queue constitutes a critical region and requires synchronization upon each access.

A key factor for successful application of dynamic scheduling techniques is the choice of a suitable granularity, i.e. the size of the tasks or groups of iterations as basis for the demand-driven allocation to threads. While a large number of small tasks results in good load balancing, the organizational overhead becomes prohibitive. Low granularity keeps the overhead within bounds, but load balancing may be insufficient. More advanced scheduling schemes address this dilemma by adapting task granularity during execution. They start with rather large tasks for low overhead in the beginning and systematically reduce task sizes for good load balancing towards approaching the final synchronization barrier. Examples are guided self-scheduling (Polychronopoulos & Kuck, 1987), factoring (Hummel et al., 1992), or the trapezoid method (Tzen & Ni, 1993). Basically, they differ in the design of the task size regression scheme.

Another important source of overhead arises from the central task queue design. With increasing task granularity and growing processor counts, the central task queue is likely to become a performance bottleneck. Even worse, data locality is usually poor because schedulers based on a central task queue do not take into account the history of tasks previously associated with some thread (Squillante & Lazowska, 1993). Since modern shared memory multiprocessor systems heavily rely on effective utilization of processor-specific cache hierarchies, more recent dynamic scheduling techniques such as locality-based dynamic scheduling (LDS) (Li et al., 1993), affinity scheduling (Markatos & LeBlanc, 1994), or adaptive affinity scheduling (Yan et al., 1997) operate on thread-specific task queues. Based on a static a-priori allocation of tasks to threads, under-utilized threads "steal" tasks from heavier loaded threads once they have completed their own a-priori assignment.

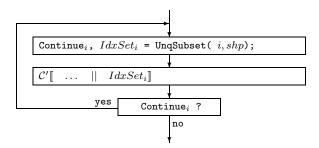

## Adapting compilation schemes for dynamic scheduling

A common characteristic of all dynamic loop scheduling techniques is the repeated allocation of tasks to individual threads. This is a prerequisite for any kind of adaptive workload balancing. Unfortunately, our multi-threaded compilation scheme  $\mathcal{CMT}$ , as defined in Section 3, associates exactly one rectangular index subspace with each worker thread. In order to support dynamic WITH-loop scheduling, we extend the compilation scheme  $\mathcal{CMT}$  as illustrated in Fig. 10. In addition to computing some iteration subspace, a scheduler provides a flag Continue, which decides whether or not the scheduler wishes to re-assign additional work to the thread later on. Once a worker thread has completed processing the assigned index subspace, it inspects the flag Continue. Depending on the value of Continue, the worker thread either continues as described in the previous section or it returns to the scheduler for assignment of further work.

Fig. 10: Extending  $\mathcal{CMT}$  for dynamic workload balancing.

#### Task selection and scheduling

Implementations of WITH-loop schedulers must address two more or less orthogonal aspects: task selection and task scheduling. Task selection combines individual elements of the global index set to tasks; task scheduling allocates entire tasks to threads. By choosing the number and size of tasks, task selection determines the granularity of task scheduling. Both task selection and task scheduling offer a wide range of design choices. Previous research on loop scheduling in general has shown that different settings require different scheduling techniques. No single approach is optimal in all cases. We have implemented two different task selectors and three different task schedulers. Their combinations provide the necessary flexibility to realize most of the loop scheduling techniques sketched out before.

The task selector Even(n) organizes the iteration space as equally sized rectangular blocks. The parameter n defines the desired number of tasks as a multiple of the number of threads. The task selector Factoring defines tasks with decreasing size according to a formula proposed in (Hummel  $et\ al.$ , 1992):

$$task\ size = \left| \frac{remaining\ iterations}{2*number\ of\ threads} \right| + 1$$

.

One task size is used for as many consecutive tasks as threads are used. The term remaining iterations refers to the number of iterations not yet allocated to tasks. Table 1 illustrates this task selector for an example of 800 iterations and four threads. In general, the factoring approach has shown to be a suitable compromise for the task granularity trade-off.

The three task schedulers are called Static, Self, and Affinity. The task scheduler Static offers the simplest implementation; it assigns tasks to threads statically in a round-robin manner. In combination with the task selector Even(1), the task scheduler Static realizes a standard block scheduling. The general case Even(n) leads to a block-cyclic scheduling and, with increasing n, to cyclic scheduling. The task scheduler Self implements a central task queue, from which worker threads obtain tasks on demand. Depending on the choice of the task selector, the task scheduler Self either implements self-scheduling or factoring. The task scheduler Affinity requires the most complex implementation. It employs an individual task queue for each thread. As long as the associated local task queue is not empty, a

| Task | Size | Task | Size | Task | Size | Task | Size |

|------|------|------|------|------|------|------|------|

| T1   | 101  | Т9   | 25   | T17  | 6    | T25  | 2    |

| T2   | 101  | T10  | 25   | T18  | 6    | T26  | 2    |

| T3   | 101  | T11  | 25   | T19  | 6    | T27  | 2    |

| T4   | 101  | T12  | 25   | T20  | 6    | T28  | 2    |

| T5   | 50   | T13  | 13   | T21  | 3    |      |      |

| T6   | 50   | T14  | 13   | T22  | 3    |      |      |

| T7   | 50   | T15  | 13   | T23  | 3    |      |      |

| T8   | 50   | T16  | 13   | T24  | 3    |      |      |

Table 1: Example application of task selector Factoring.

thread always selects the next task pre-assigned to it. After having completed all statically pre-assigned tasks, a thread tries to identify heavily loaded threads with non-empty local task queues and "steals" tasks from them. Affinity scheduling offers all load balancing opportunities of a dynamic loop scheduler while avoiding the drawbacks of a central task queue design, i.e. frequent synchronization on access, low data locality, and the potential for becoming a scalability bottleneck.

For the time being, task selector Even(1) and task scheduler Static are used as defaults. However, for experimental purposes programmers are free to choose any combination of task selector and task scheduler either on a program-wide basis or for individual WITH-loops. Based on experimental experience, we envision compiler heuristics that implicitly select the most appropriate combination of task selector and task scheduler in the future.

## 5 Enhancing the execution model

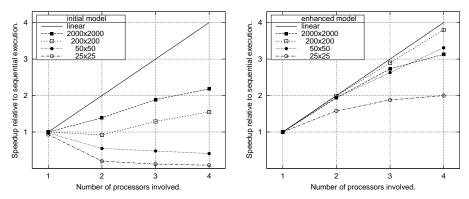

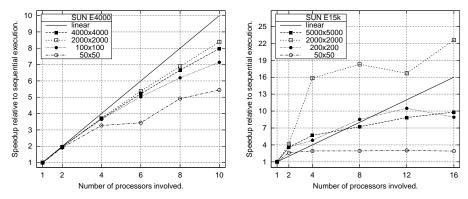

The compilation scheme  $\mathcal{CMT}$ , as defined in Section 3, addresses individual WITH-loops. In compiled code, there is no connection between multi-threaded execution of consecutive WITH-loops. This limited scope facilitates the definition of a basic compilation scheme, yet it excludes any optimization across multiple WITH-loops. Following the multi-threaded execution of one WITH-loop, all worker threads terminate during synchronization. The same number of worker threads is again created for the multi-threaded execution of the following WITH-loop. Program execution is a sequence of steps alternatingly performed in single-threaded and in multi-threaded mode, as illustrated on the left hand side of Fig. 11.

This fork/join execution model is conceptually simple. Synchronization and communication events are confined to thread creation and thread termination. Worker threads do not interact with each other at all. However, the price for simplicity is excessive runtime overhead due to frequent creation and termination of threads. Although the associated costs are much smaller than those for process creation and termination, they are still prohibitive for successful parallelization.

A solution which combines the conceptual simplicity of the fork/join approach with an efficient execution scheme is shown on the right hand side of Fig. 11. In the

Fig. 11: Comparison of pure and enhanced fork/join execution models.

enhanced fork/join model, the desired number of worker threads is created once at program start, and all threads remain active until the whole program terminates. Two tailor-made barriers, the *start barrier* and the *stop barrier*, realize all necessary synchronization among threads.

After creation, worker threads immediately hit a start barrier. As soon as the master thread encounters the first WITH-loop, the start barrier is lifted. The worker threads thereupon activated share the computation of the WITH-loop, exactly as in the pure fork/join model. Unlike in the pure fork/join model, the master thread temporarily turns itself into a worker thread and joins the other threads in the cooperative execution of the WITH-loop. Regular worker threads that have completed their individual computations pass the following stop barrier and, with nothing else to do, immediately move on to the next start barrier. After having finished its own assignment of work, the master thread waits at the stop barrier for the longest-running worker thread to arrive. Only then the master thread proceeds with subsequent (sequential) computations.

# Implementing synchronization barriers

The combination of a stop barrier and a subsequent start barrier represents a full barrier synchronization, which is known to cause considerable runtime overhead with increasing numbers of threads (Cohen *et al.*, 1994; Hill & Skillicorn, 1998). Therefore, careful design and efficient implementation of start and stop barriers are crucial for performance. Fig. 12 shows our implementation of the start barrier. It is based on a global flag, which is shared by all threads, and on one local flag

within the scope of each worker thread. All flags are statically initialized to zero. Worker threads executing START\_BARRIER\_WAIT block on the condition of the empty WHILE-loop. By inverting the global flag during execution of START\_BARRIER\_LIFT, the master thread activates the worker threads. Having passed the barrier, worker threads copy the new value of the global flag into their local flags to prepare execution of subsequent instances of the start barrier.

```

START_BARRIER_WAIT( )

{

while (local_flag == global_flag);

local_flag = global_flag;

}

START_BARRIER_LIFT( )

{

global_flag = 1 - global_flag;

}

```

Fig. 12: Implementation of start barriers.

Inverting the global flag while worker threads continuously poll on it, is a race condition. However, this race condition is without problems. On the one hand, only the master thread has write access to the global flag. On the other hand, worker threads only reflect the change of the flag's value, not the specific state of the memory location. By exploiting a controlled race condition this start barrier implementation completely avoids expensive thread synchronization mechanisms such as mutex locks or semaphores. The sole assumption made on the memory consistency model is that write operations issued by one processor are observed by others.

One may argue that iteratively reading the global flag in very short time intervals generates heavy contention on the shared memory. In fact, the opposite is true for modern multiprocessors with processor-specific cache memories and hardware cache coherence. As soon as an individual worker thread hits the start barrier, it loads the global flag into the local cache of the processor it is currently running on. Afterwards, it only accesses the local cache when polling on the global flag. However, when the master thread inverts the global flag and writes its new value back to memory, the cache coherence mechanism invalidates the local copies in all other caches. Only then worker threads reload the global flag from memory and proceed beyond the start barrier. Each thread performs at most two main memory accesses during execution of the start barrier.

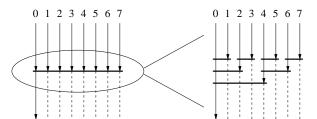

Our stop barrier implementation follows the same approach as the start barrier. It employs a global vector of flags, one for each thread. To improve scalability, the stop barrier is implemented as a binary tree of pairwise synchronizations, as illustrated in Fig.13. After having set its associated ready flag, a worker thread with an odd ID immediately passes the stop barrier to hit the subsequent start barrier. Each thread with an even ID n waits for thread n+1 to complete before it

either passes the stop barrier itself if its ID is not a multiple of four, or it continues waiting for thread n + 2 otherwise, and so on.

Fig. 13: Organization of tree-structured stop barriers.

The basic realization of the stop barrier has been refined several times. For example, threads which synchronize with multiple other threads may do so in any order. In the case of fold-WITH-loops, final folding operations are integrated into the stop barrier and performed as soon as two threads synchronize with each other. This solution interleaves synchronization overhead with productive computations.

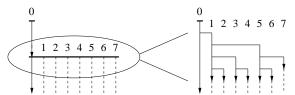

## Implementing thread creation

In the enhanced fork/join model the performance impact of thread creation decreases with growing program execution time. Nevertheless, it makes sense in principle to care for efficient implementations. In a straightforward approach, the master thread creates all worker threads, one after the other. Execution of productive code is delayed by a time which grows linearly with the number of threads. We can reduce this initial delay by having the worker threads participate in thread creation. With a binary tree thread creation scheme, the initial delay is only  $\mathcal{O}$  (log NUM\_THREADS).

Fig. 14: Organization of thread creation phase.

Yet, we can do even better by exploiting the observation that many programs have a sequential startup phase. For example, they read input data from files or they initialize data structures. Therefore, it makes sense to exclude the master thread from worker thread creation. As sketched out in Fig. 14, the master thread only creates a single worker thread and immediately starts execution of productive code. Instead of the master thread, the first worker thread initiates a binary tree thread creation scheme. Thread creation almost completely overlaps with a program's sequential startup phase and effectively reduces the thread creation overhead to  $\mathcal{O}(1)$ .

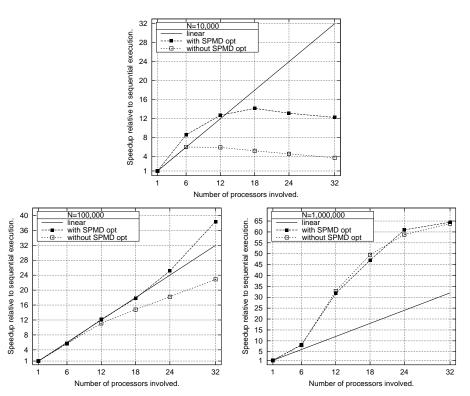

# 6 SPMD optimization

The enhanced fork/join execution model significantly reduces synchronization costs by replacing thread creation and thread termination by less expensive start and stop barriers, respectively. Nevertheless, program execution stalls at each stop barrier until arrival of the longest-running worker thread. Start and stop barriers are still major sources of overhead. In this section we describe optimization techniques which aim at eliminating synchronization barriers. Besides avoiding the cost immediately associated with the execution of the barrier code and the need to wait for the longest-running worker thread, larger regions of parallel execution also render the scheduling techniques discussed in Section 4 more effective.

# Introducing SPMD skeletons

So far, WITH-loops are used to describe both a computational task and a coordination behaviour, i.e. the organization of the parallel execution of the given task by multiple threads. Creating regions of parallel execution that stretch over several WITH-loops requires explicit separation of these two aspects. Therefore, we introduce *SPMD skeletons* as intermediate representations of the coordination behaviour of regions of parallel execution. Within such regions, which may contain multiple WITH-loops, program execution follows the "Single Program, Multiple Data" approach, hence the name. Our SPMD skeletons have the form

The fourth parameter CODE refers to a sequence of WITH-loops embedded in a joint region of parallel execution without synchronization and communication inside. The other three parameters provide the necessary information to generate multi-threaded code from the spmd skeleton without identifying the WITH-loops inside. The first parameter USE contains the set of argument variables, which have to be communicated to worker threads when initiating parallel program execution. The second parameter MAP denotes a set of pairs each consisting of the result variable of an embedded genarray-WITH-loop and the associated shape specification. Similarly, the third parameter FOLD denotes a set of pairs each consisting of the result variable of an embedded fold-WITH-loop and the associated fold operation. Fig. 15 shows the transformation scheme SPMD, which introduces spmd skeletons around individual WITH-loops.

# Merging SPMD skeletons

Introducing spmd skeletons around WITH-loops alone does not alter the multithreaded code generated. We merely lay the foundation for a subsequent optimization step, which tries to merge several spmd skeletons into a single one. This optimization is formalized by the transformation scheme  $\mathcal{MERGE}$ , which is shown in Fig. 16. The definition of  $\mathcal{MERGE}$  is based on guarded transformation rules. Predicate expressions following vertical bars restrict transformation rules to specific conditions. The predicate "otherwise" matches whenever none of the previous

```

gen_n : expr_n

genarray( shp);

\{shp\} \cup \bigcup_{i=1}^{n}

a = spmd(

\{ [a, shp] \}

with

gen_1 : expr_1

gen_n : expr_n

genarray( shp); );

\mathcal{SPMD}[\![Rest]\!]

gen_n : expr_n

fold( fold_op, neutral);

\{ [a, fold\_op] \},

gen_1 : expr_1

gen_n : expr_n

fold( fold_op, neutral); );

\mathcal{SPMD}[Rest]

SPMD[a = expr; Rest]

= expr; SPMD[Rest]

SPMD[return(a_0, ..., a_k);]

return( a_0, ..., a_k);

```

Fig. 15: Embedding WITH-loops within spmd skeletons.

rules was applicable.  $\mathcal{MERGE}$  identifies pairs of spmd skeletons which are directly adjacent in a sequence of assignments and which are free of data dependencies. Such pairs are combined into a single spmd skeleton with multiple return values. An example which illustrates both the introduction of spmd skeletons and the merging step can be found in Fig. 17. For reasons of simplicity, only the free variables of the generator-expression pairs are shown rather than complete WITH-loops.

# Compilation of SPMD skeletons

The SPMD optimization may lead to complex spmd skeletons containing many different WITH-loops. Nevertheless, the compilation schemes described in Section 3

```

\begin{split} \mathcal{MERGE} \begin{bmatrix} A &= \text{spmd}(\ USE_A,\ MAP_A,\ FOLD_A,\ CODE_A); \\ B &= \text{spmd}(\ USE_B,\ MAP_B,\ FOLD_B,\ CODE_B); \\ Rest \end{bmatrix} \\ &\Longrightarrow \mathcal{MERGE} \begin{bmatrix} A,\ B &= \text{spmd}(\ USE_A \cup\ USE_B,\ MAP_A \cup\ MAP_B,\ FOLD_A \cup\ FOLD_B,\ CODE_B; \\ Rest \end{bmatrix} \\ &\mid A \cap USE_B &= \emptyset = A \cap B \\ &\Longrightarrow A &= \text{spmd}(\ USE_A,\ MAP_A,\ FOLD_A,\ CODE_A); \\ \mathcal{MERGE} \begin{bmatrix} B &= \text{spmd}(\ USE_B,\ MAP_B,\ FOLD_B,\ CODE_B); \\ Rest \end{bmatrix} \\ &\mid OTHERWISE \end{split}

```

Fig. 16: SPMD optimization scheme  $\mathcal{MERGE}$ .

```

A = with ... D ... k ... C ... genarray(shp_A);

B = with ... C ... x ... y ... genarray(shp_B);

d = with ... k ... x ... z ... fold( fun, neutr);

A = spmd( \{shp_A, D, k, C\},

{[A, shp_A]},

{ },

A = with ... D ... k ... C ... genarray( shp_A); );

B = spmd( \{shp_B, C, x, y\},

{[B, shp_B]},

B = with ... C ... x ... y ... genarray(shp_B); );

d = spmd( \{neutr, k, x, z\},

{ },

{[d, fun]},

d = with ... k ... x ... z ... fold(fun, neutr););

A, B, d = spmd( \{shp_A, shp_B, D, k, C, x, y, z, neutr\},

{[A, shp_A], [B, shp_B]},

{[d, fun] },

A = with ... D ... k ... C ... genarray(shp_A);

B = with \dots C \dots x \dots y \dots genarray(shp_B);

d = with ... k ... x ... z ... fold( fun, neutr); );

Fig. 17: Example illustrating the SPMD optimization.

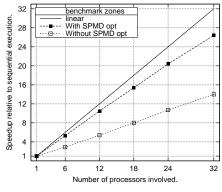

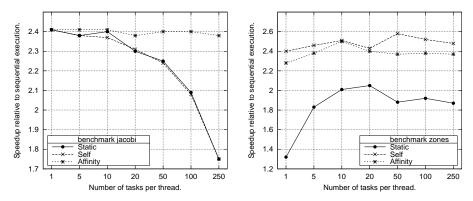

```